Basic Leiterplatten

Ein-, doppelseitige und Multilayer-Leiterplatten

Einseitige, doppelseitige und Multilayer-Leiterplatten

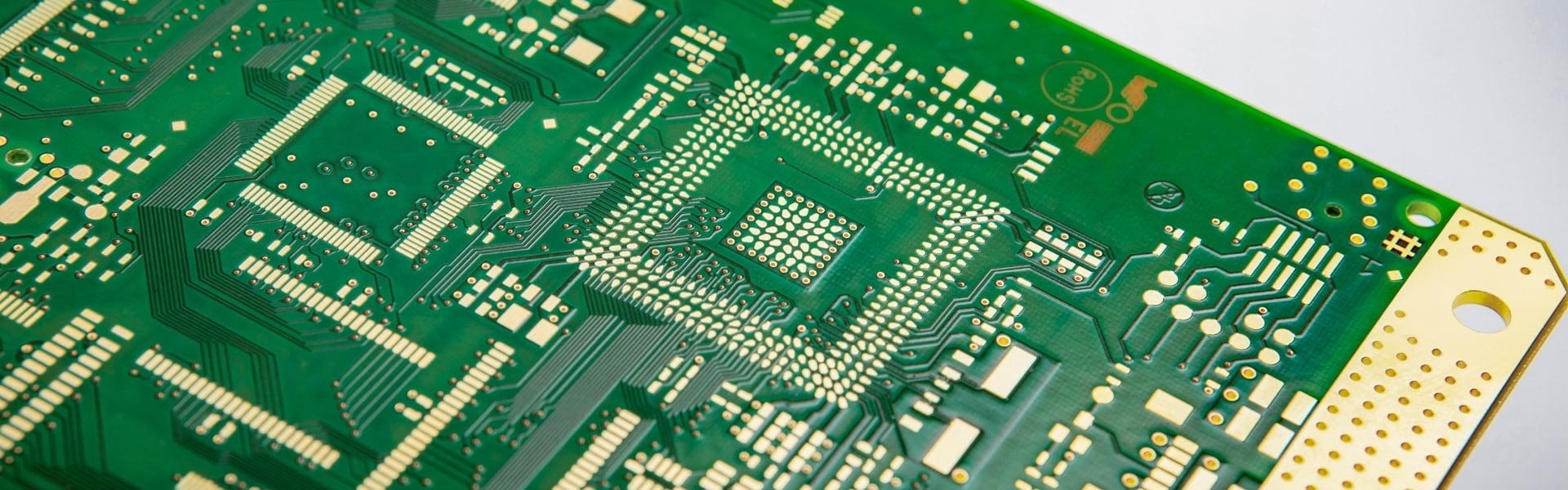

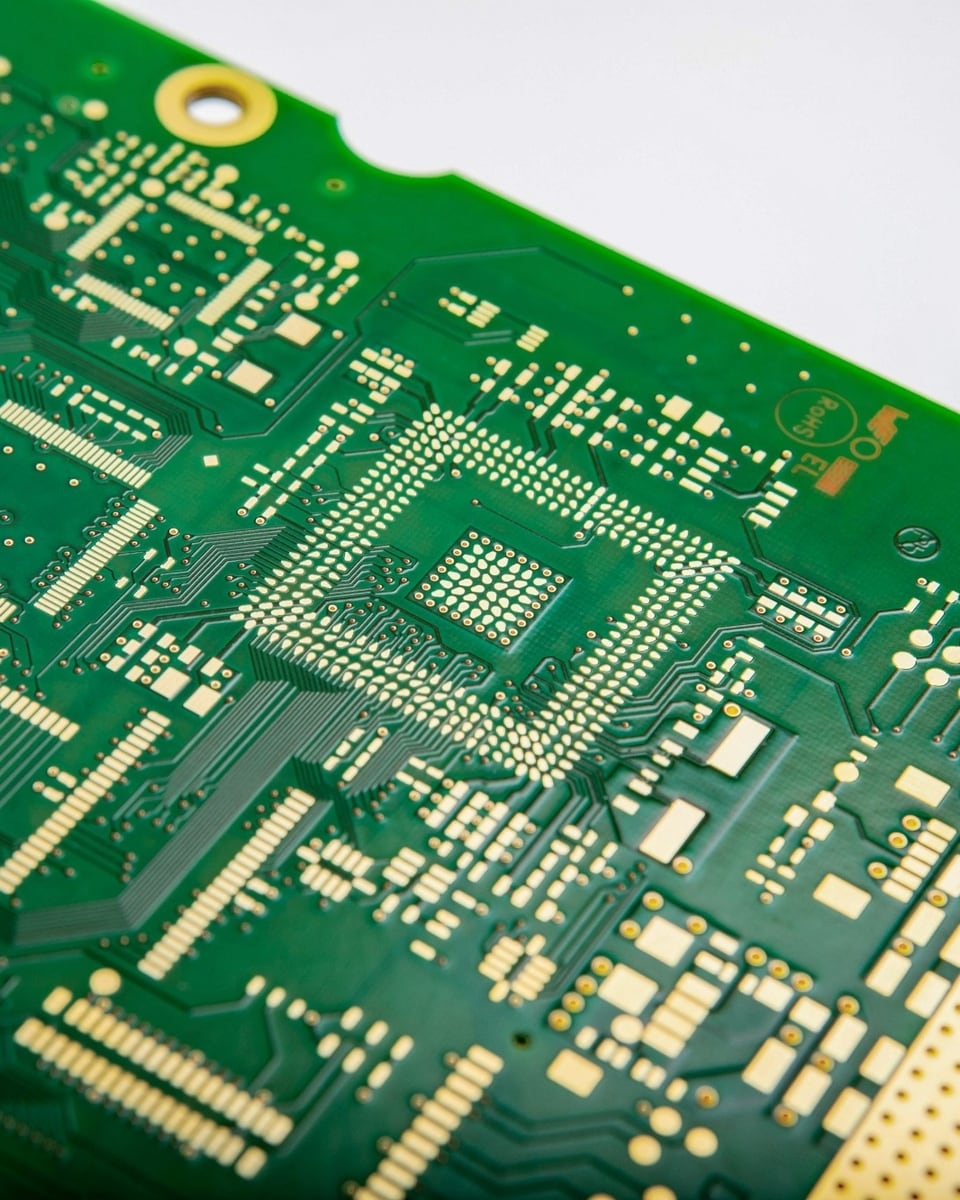

Unter BASIC Technologie fassen wir einseitige, doppelseitige und Multilayer-Leiterplatten zusammen. Jede Leiterplatte ist etwas Besonderes, ein Unikat – Ihre Schöpfung, von uns hergestellt. Hergestellt aus Basismaterial in FR4-Qualität bildet diese Technologie das zuverlässige Fundament für viele Anwendungen, beispielsweise aus Industrie, Medizintechnik, Automotive und Aerospace.

Mit metallisierten, durchgehenden Bohrungen (PTH = Plated Through Hole) als Bauteilebohrungen und als elektrische Verbindung zwischen den Kupferlagen können damit verschiedenste Elektronikkomponenten bis zur BGA-Bauform mit einem Anschlussraster von 0,8 mm verdrahtet werden. Damit wird Ihr Schaltungsplan und Ihre individuelle Lösung Realität.

Gut – besser – Standard: Standards sind auch hier die Basis für Qualität und Effizienz in Form von bewährten Lagenaufbauten und Designregeln. Sichern Sie Fehlervermeidung und Produktivitätserhöhung beim Design, die Herstellbarkeit sowie die Zuverlässigkeit der Leiterplatte in der Anwendung.

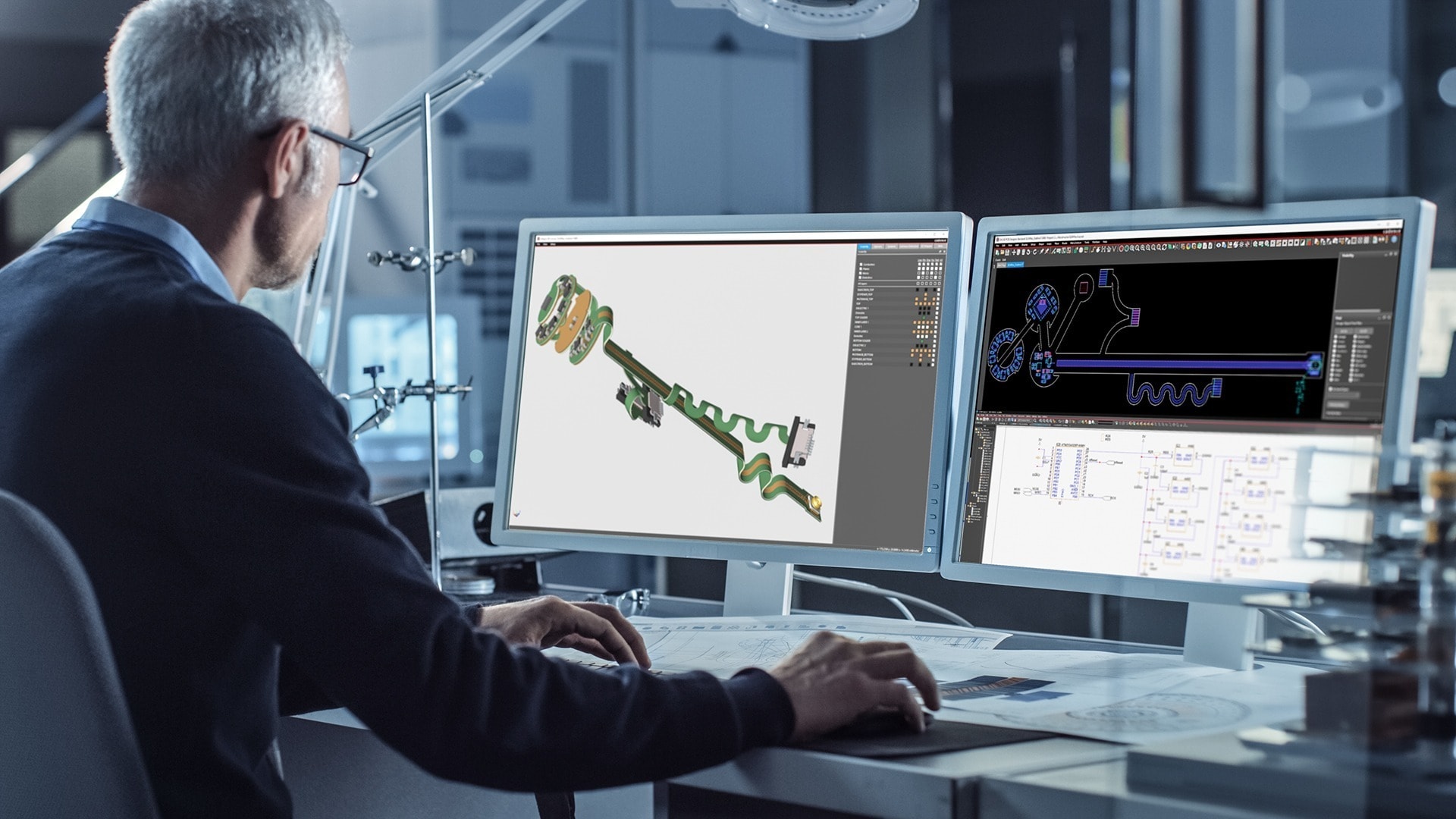

Verlassen Sie sich auf unsere Erfahrung und nutzen Sie unsere Standard Leiterplatten Lagenaufbauten, die auch in digitaler Form für viele EDA-Tools zur Verfügung stehen.

Sie haben weitergehende Anforderungen? Dann bieten wir Ihnen weitere innovative und maßgeschneiderte Technologien an:

Lassen Sie sich von uns persönlich beraten, um basierend auf Ihren spezifischen Anforderungen die verfügbaren Standardoptionen sowie die wichtigsten Designparameter für Materialien und Fertigungsprozesse zu definieren.

Vorteile der Würth Elektronik BASIC Technologie

Wir erklären im Video die verwendeten Materialien und die grundsätzlichen Prozessschritte. Anwendungsbeispiele veranschaulichen die vielfältigen Einsatzfelder von Leiterplatten.

Relevante Parameter für fertigungsgerechtes Leiterplatten-Design

Moderne Leiterplatten-Lösungen sind mehr als nur Verbindungselemente. Sie sind der Schlüssel zum Fortschritt in der Elektronik. Vor diesem Hintergrund unterstützen wir unsere Kundinnen und Kunden aktiv bei der Entwicklung und bieten darüber hinaus eigene Systemlösungen mit elektronischen Funktionen.

In unseren BASIC Design Rules finden Sie alle Parameter, die Sie beim Design und Layout von Leiterplatten beachten sollten.

Darüber hinaus haben wir im Design Guide Plugging-Filling-Tenting neben grundlegenden Begriffsdefinitionen auch die einzelnen Ausführungen von Vias mit den jeweiligen Zielen übersichtlich für Sie zusammengefasst. So finden Sie für jeden Ihrer Anwendungsfälle die richtige Lösung – innerhalb der IPC-4761 und darüber hinaus.

Sie möchten unsere Design Guides und Design Rules als übersichtliches Technologie-Poster downloaden? Das Poster bietet Ihnen die wichtigsten Informationen rund um effizientes Leiterplatten-Design.

Relevante Parameter für fertigungsoptimiertes Leiterplatten-Design

Moderne Leiterplatten-Lösungen sind mehr als nur Verbindungselemente. Sie sind der Schlüssel zum Fortschritt in der Elektronik. Vor diesem Hintergrund unterstützen wir unsere Kundinnen und Kunden aktiv bei der Entwicklung und bieten darüber hinaus eigene Systemlösungen mit elektronischen Funktionen.

In unseren BASIC Design Rules finden Sie alle Parameter, die Sie beim Design und Layout von Leiterplatten beachten sollten.

Darüber hinaus haben wir im Design Guide Plugging-Filling-Tenting neben grundlegenden Begriffsdefinitionen auch die einzelnen Ausführungen von Vias mit den jeweiligen Zielen übersichtlich für Sie zusammengefasst. So finden Sie für jeden Ihrer Anwendungsfälle die richtige Lösung – innerhalb der IPC-4761 und darüber hinaus.

Die minimalen Strukturen haben sich teilweise sogar verbessert, in keinem Fall verschlechtert.

Allerdings hat sich die Herleitung oder Darstellung verändert:

Bezüglich der Frage stellt es sich so dar:

Innenlagen können einfach durch Ätzen strukturiert werden, das Kupferdesign wird dabei durch Resist abgedeckt. Im Prozess der Außenlagen müssen neben der reinen Strukturierung zusätzlich die Bohrungen (PTHs) metallisiert werden, um die elektrische Verbindung zwischen den Kupferlagen herzustellen. Dazu wird Kupfer in der Bohrungshülse und auf den Außenlagen abgeschieden. Für die Fotostrukturierung muss deshalb der Prozess invertiert werden, die Bohrungen und das Kupferdesign sind für den Kupferaufbau offen und der Resist verhindert einen Kupferaufbau an den Stellen, wo im Endprodukt kein Kupfer sein soll.

Diese Frage wird allgemein sehr kontrovers diskutiert, es gibt Argumente dafür und dagegen. Aus unserer Erfahrung bringt das Entfernen keine signifikanten Verbesserungen hinsichtlich der Herstellbarkeit und Herstellkosten. Hinzu kommt eine geringere Verankerung und Stabilität der Hülse, was sich bei thermo-mechanischem Stress, also beispielsweise Lötzyklen oder Temperaturwechseln im Feldeinsatz, negativ auswirken kann. Bei der STARR.flex-Technolgie ist das Entfernen von non-used/non-functional Pads auf den Polyimid-Lagen unbedingt zu unterlassen – ansonsten kann die Zuverlässigkeit stark beeinträchtigt werden!

Grundsätzlich ist in diesem Vergleich 1 oz. zu ½ oz. (35 µm Kupferfoliendicke zu 17,5 µm) die dünnere Kupferfolie kostengünstiger. Gleichzeitig sind mit der dünneren Foliendicke kleinere Abstände leichter herzustellen, die höhere Ausbeute wirkt ebenfalls kostensenkend.

Die Kupferverteilung sollte grundsätzlich so gleichmäßig wie möglich sein. Für Signallagen ist der Flächenanteil des Kupfers geringer als für Planes, sollte aber im Bereich 40 bis 60 % liegen. Größere Flächen ohne Kupfer sollten gefüllt und auf ein definiertes Potenzial gelegt werden. Ein hoher Flächenanteil verbessert beispielsweise die Entwärmung durch Wärmeverteilung und Wärmeableitung. Eine hohe Gleichmäßigkeit der Kupferverteilung ist wichtig für die Herstellbarkeit mit geringen Dicken- und Ätztoleranzen sowie einer geringen Wölbung/Verwindung der Leiterplatte.

Die IPC-2221 definiert, dass die Leiterbreite am Fuß gemessen wird, siehe IPC-2221B Bild 10.1. Die Fertigungsdaten für den Fotoresist sind also entsprechend modifiziert mit dem Ziel, dass nach dem Ätzen die gewünschte Endbreite laut Kundendaten erreicht werden.

Prepreg (und Kupferfolie) außen ist einfacher und kostengünstiger, der Layerstack braucht einen Kern weniger. Prepreg und Kupferfolie tragen keine Strukturen und müssen deshalb nicht zu den Innenlagen registriert werden. Bei außenliegenden Kernen müssen deren innere Lagen vor dem Verpressen strukturiert und für das Verpressen registriert werden, die Außenseiten müssen für die Folgeprozesse dagegen komplett mit Kupfer bedeckt bleiben. Der Herstellprozess mit Folienverpressung ist also einfacher als mit Kernverpressung.

Immer den Enddurchmesser, nur bei Einpressbohrungen wird zusätzlich der Werkzeugdurchmesser definiert.

Mit dem Standardprozess beträgt die Kantenabdeckung mindestens 5 µm. Mit Mehrfachbeschichtung wird der Lack überall dicker, mit der s.mask-Technologie kann die Schichtdicke lokal erhöht werden.

Das Material für Prepregs und Kerne in einem Aufbau ist bei Würth Elektronik immer sortenrein, also bei BASIC Multilayer aus FR4 eines Herstellers. Die Prepregs sind aus demselben Material wie die Kerne, jedoch ist das Harz nicht vollständig ausgehärtet („B-stage“). Wie bei der Herstellung der Kerne (aus Prepregs und Kupferfolie) wird das Prepreg-Harz bei der Multilayer-Herstellung erst beim Multilayer-Verpressen vollständig ausgehärtet (vernetzt, „C-stage“).

Ja, auch dann sollten die Leiter und Kupferstrukturen vor Berührung und Verschmutzung geschützt werden. Lötstopplack hat also eine Funktion nicht nur für den Lötprozess, sondern auch für den Einsatz der Leiterplatte.

Starten Sie schneller mit Ihrem Layout – dank standardisierter Lagenaufbauten

Mit diesen Stackups verwenden Sie automatisch marktübliche und kostenoptimierte Standards und vermeiden teure Sonderaufbauten. Außerdem wird eine qualitativ hochwertige und kostengünstige Herstellung mit kürzeren Lieferzeiten ermöglicht, da lagerhaltige Materialien verwendet werden und standardisierte Produktionsabläufe eingehalten werden.

Unsere Standards bieten eine Basiskupferdicke von 18 µm oder 35 µm auf den Innenlagen. Für feine Strukturen und gute Herstellbarkeit sind 18 µm zu bevorzugen.

Hier finden Sie unsere BASIC Standard Lagenaufbauten in digitaler Form zum Import in Ihre EDA-Software und als PDF:

BASIC Leiterplatten

Wir tauchen ein in die faszinierende Welt der Leiterplatten und lernen die BASIC Technologie kennen. Woraus bestehen BASIC Leiterplatten? Was ist ein Multilayer? Und wie werden die vielen Schichten, wenn auch nicht 1.000, hergestellt?

Unser “Mr. Webinar” Andreas Schilpp beantwortet ausführlich die TOP 3-Fragen aus den letzten 100 Webinaren.

In unserem Webinar erfahren Sie mehr über:

Das erste Webinar Ihrer Top 3, ursprünglich im Mai 2013 angeboten, ist aktueller denn je: Vor kurzem wurden die Würth Elektronik BASIC Design Rules überarbeitet und neu strukturiert.

Wussten Sie beispielsweise, dass für die Herstellprozesse von Leiterplatten der Parameter „Leiterbreite“ ziemlich unbedeutend ist?

Erfahren Sie in diesem Webinar mehr über

Wussten Sie beispielsweise, dass der Wechsel zu einem etwas kleineren Bohrer unter Umständen einen wesentlich höheren Preis der Leiterplatte verursachen kann? Interessant ist das Webinar für Entwicklung, Einkauf und Management. Erhalten Sie einen Einblick in die Verknüpfung des PCB Designs mit den Auswirkungen für die Leiterplattenfertigung und den dabei anfallenden Kosten. Wir geben Hinweise auf die generelle Kostenstruktur einer Leiterplatte mit Blick auf deren Layout und Geometrie.

Die Leiterplatte wird allgemein unterschätzt. Funktional trägt und verbindet sie elektronische Bauteile und setzt dadurch den elektrischen Schaltplan und seine Funktionen in Hardware um. Sie wird damit zunehmend selbst zum strategisch wichtigen Bauteil für das Gesamtsystem.

Materiell ist die Leiterplatte ein sehr komplexes Konstrukt, hergestellt durch eine Vielzahl von sequenziellen Prozessen aus unterschiedlichsten Materialien, die auch für die Weiterverarbeitung und die geplante Anwendung geeignet sein müssen.

Das Verständnis hierfür hilft beim Leiterplattendesign, um die Anforderungen aus dem Pflichtenheft erfolgreich im Design umsetzen zu können und das Wissen hilft ebenso bei der Kommunikation mit dem Leiterplattenhersteller.

Ihr Kontakt zu uns