# **IMPEDANCE IS FOR EVERYONE!**

Andreas Dreher, FAE

WURTH ELEKTRONIK MORE THAN YOU EXPECT

### **SPEAKER INTRODUCTION**

#### Andreas Dreher

Technical Project Management

- HDI-Design

- Signal Integrity & High Speed

Since 2003 at Würth Elektronik CBT

Phone +49 7622 397-133

Mail andreas.dreher@we-online.com

**Andreas Dreher** Field Application Engineer Technical Project Management

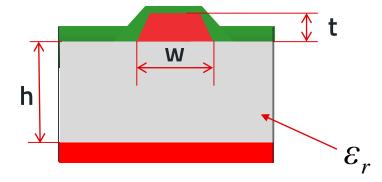

### <u>IMPEDANCE – INTRODUCTION</u>

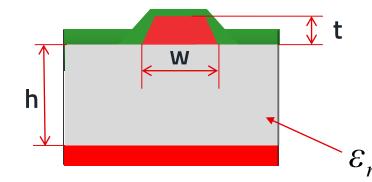

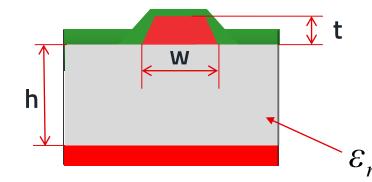

Surface Microstrip - IPC-2141

$$Z_0 = \frac{87.0}{(\varepsilon_r + 1.41)^{\frac{1}{2}}} \ln \left[ \frac{5.98h}{0.8w + t} \right]$$

$Z_0$  = Impedance

$E_r = Dk = Dielectric Constant$

h = Dielectric Thickness

w = Track Width

t = Track Thickness

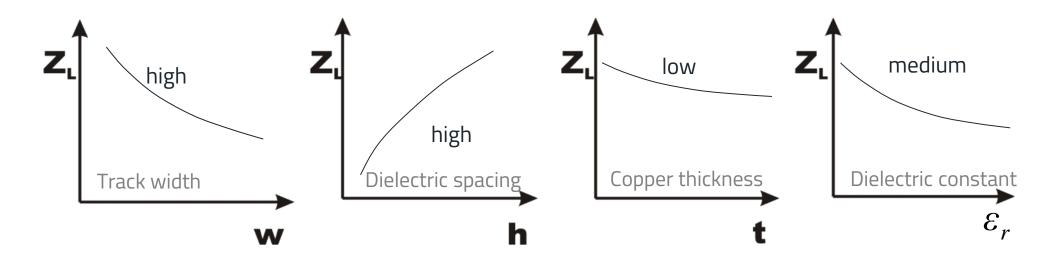

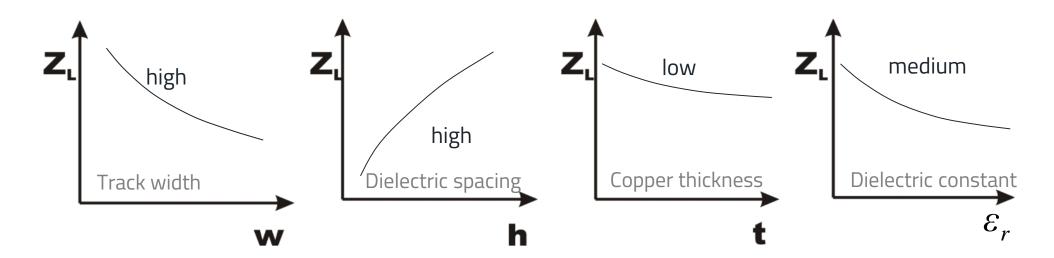

### <u>IMPEDANCE – INFLUENCING FACTORS</u>

$Z_1$  = Impedance

$E_r = Dk = Dielectric Constant$

h = Dielectric Thickness

w = Track Width

t = Track Thickness

w+h = Designer + PCB manufacturer

t = Electroplating process, base copper

$\varepsilon_r$  = Base Material

### <u>IMPEDANCE – INTRODUCTION</u>

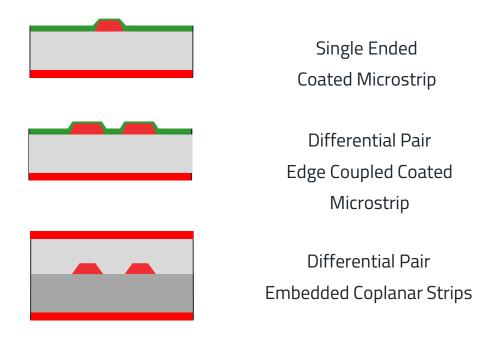

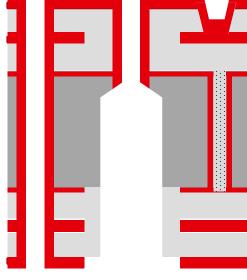

#### Types of Struktures

And many, many more...

**SUPPORT**: If you need an Impedance controlled Stack up feel free to contact us hdi@we-online.com

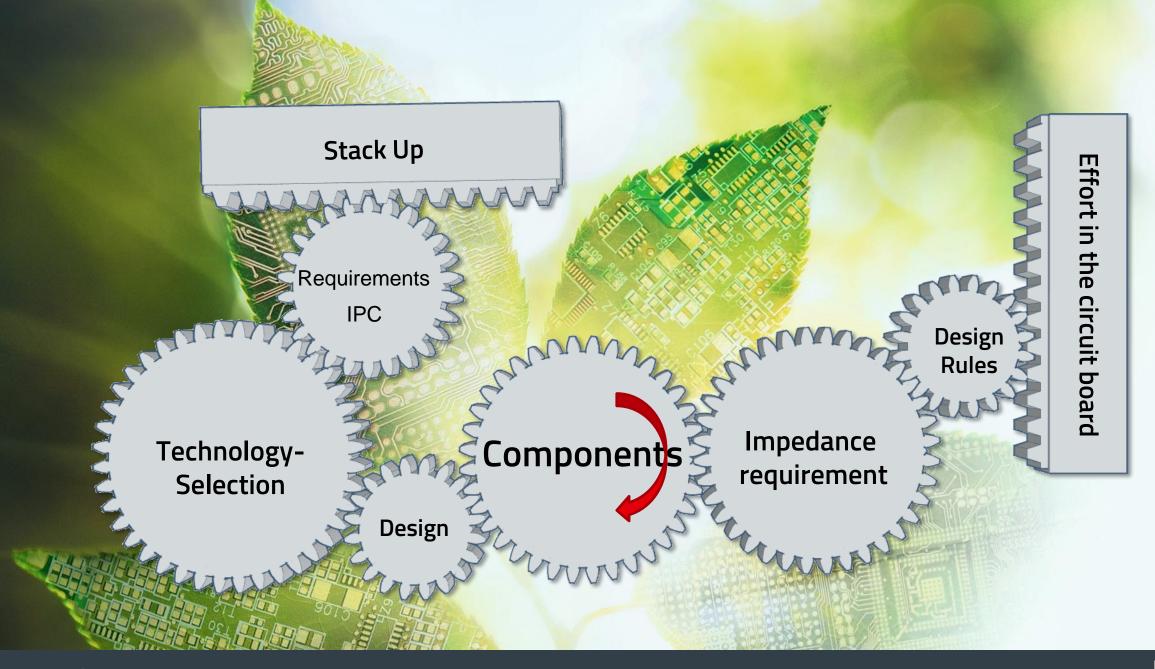

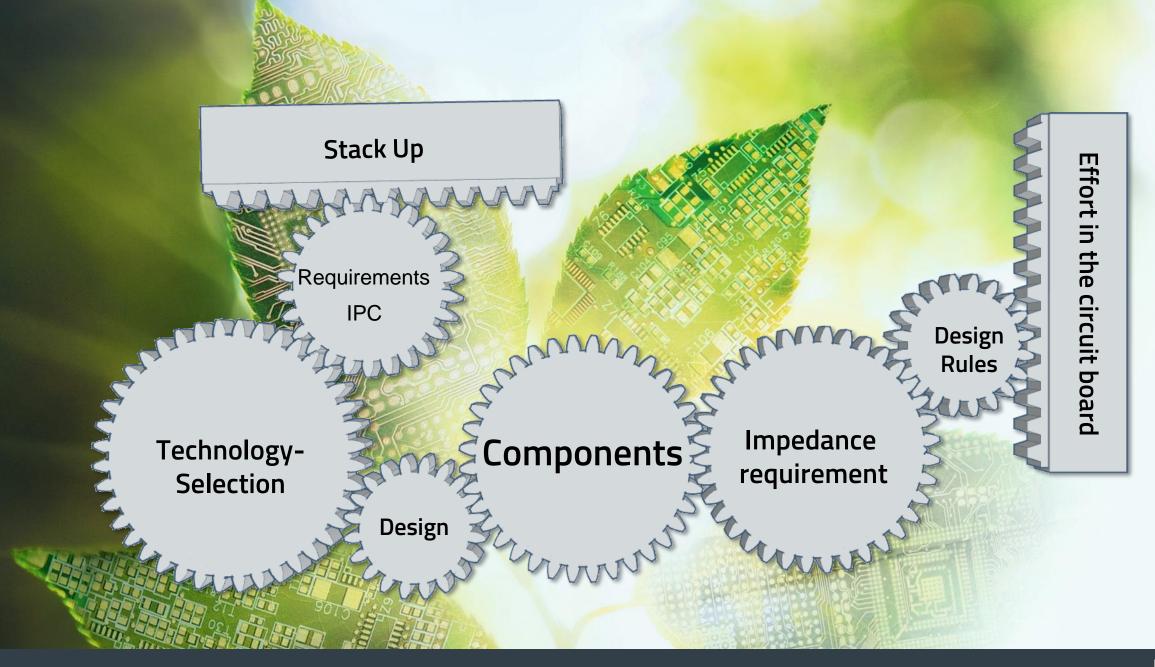

### **IMPEDANCE REQUIERMENTS**

#### Defined by Component choice

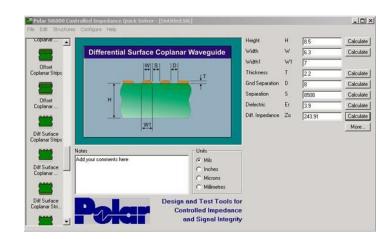

Impedance Calculation

- Material Selection

- Design Rules

- Process Tolerance

Impedance Measurement

Process Control

HIGHSPEED Measurement "Atlas"

- Helping customer with

- Material Choice

- Design Rules

- Research & Development

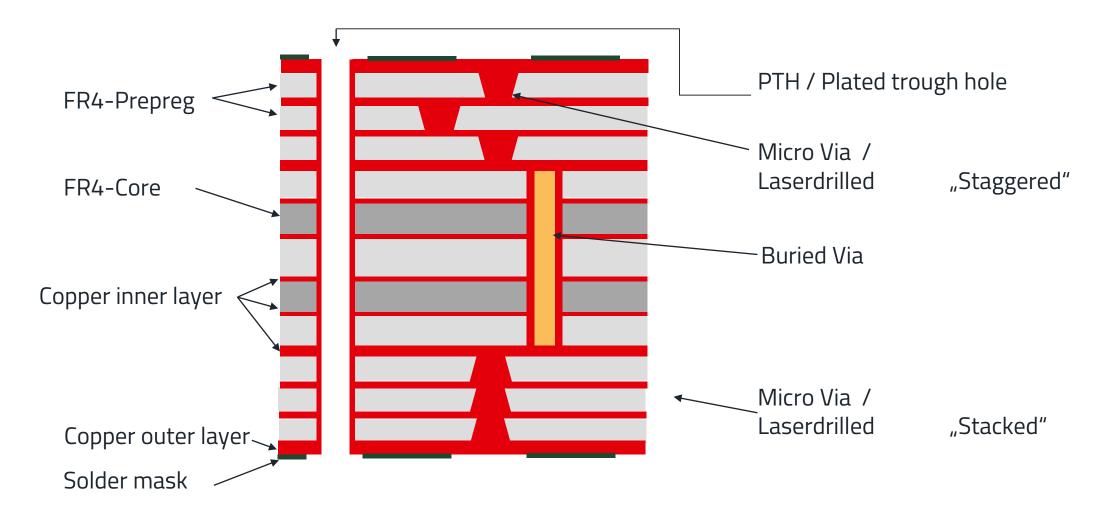

### **OVERVIEW STACKUP**

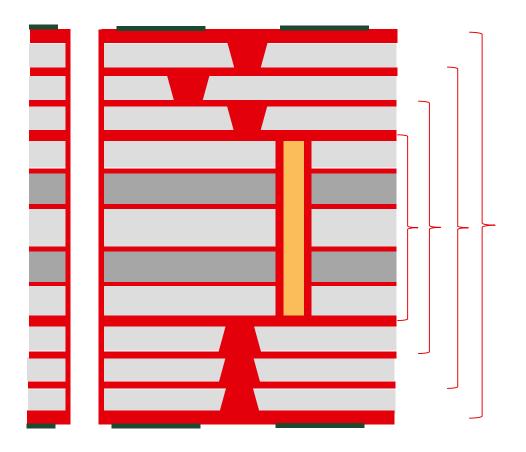

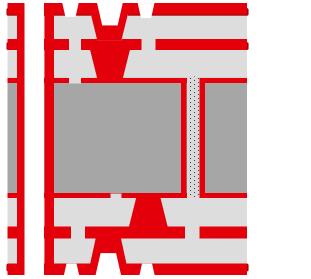

HDI12 **3-6b-3**

## **CONSTRUCTION OF A HDI PCB**

HDI12 **3-6b-3**

6x Galvanic Processes

5x Photo Processes

4x Press cycles

### **HDI MICRO VIA**

#### Technology Choice

"Staggered" Micro Via

Copper filled

Filling Resin filled

Prepreg Resin filled

"Stacked" Micro Via

Early discussion between Project Partners results in Potential multiplication

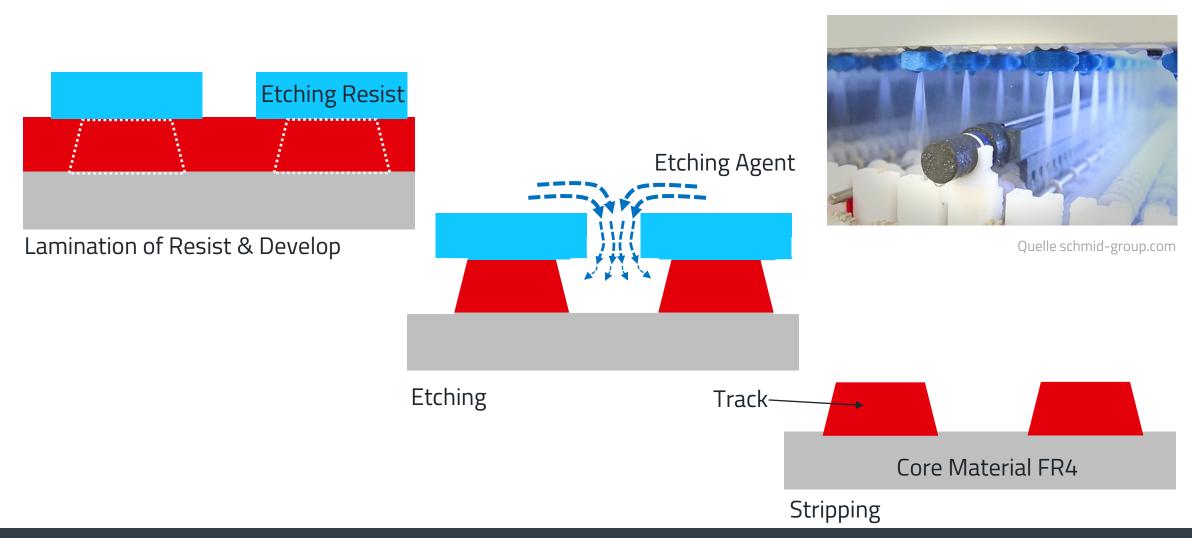

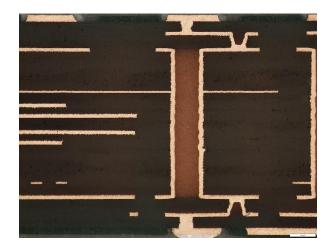

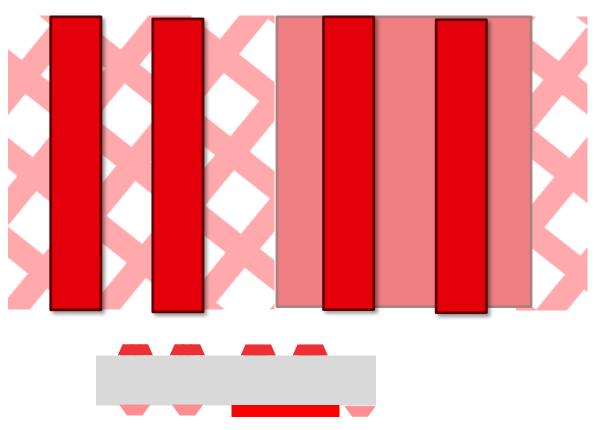

## **BASICS: PRODUCTION OF A PCB – INNER LAYERS**

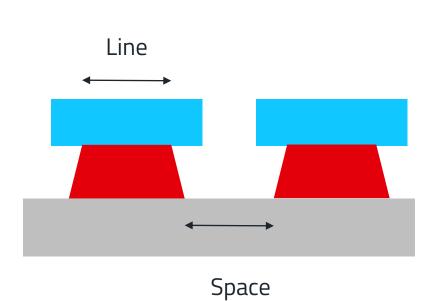

## **CORELATION BETWEEN COPPER THICKNESS AND LINE WIDTH**

| Outer layers – conductor spacing |                                       |             |               |                               |                               |  |

|----------------------------------|---------------------------------------|-------------|---------------|-------------------------------|-------------------------------|--|

| Starting foil                    | Minimum copper thickness <sup>1</sup> |             | Nominal final | Minimum                       | Minimum                       |  |

| thickness                        | IPC-class 1, 2                        | IPC-class 3 | thickness     | conductor<br>spacing Standard | conductor<br>spacing Advanced |  |

| 8,5 µm [1/4 oz.] <sup>2</sup>    | 26,2 μm                               | 31,2 µm     |               | 100 µm                        | 75 µm                         |  |

| 12 μm [3/8 oz.] <sup>2</sup>     | 29,3 μm                               | 34,3 μm     |               | 100 µm                        | 80 µm                         |  |

| 17,1 µm [1/2 oz.]                | 33,4 µm                               | 38,4 µm     | 35 µm         | 120 µm                        | 100 µm                        |  |

| 34,3 µm [1 oz.]                  | 47,9 μm                               | 52,9 μm     | 70 µm         | 180 µm                        | 160 µm                        |  |

| 68,6 µm [2 oz.]                  | 78,7 µm                               | 83,7 μm     | 105 µm        | 275 μm                        | 225 µm                        |  |

| 102,9 μm [3 oz.]                 | 108,6 µm                              | 113,6 µm    |               | 390 µm                        | 320 µm                        |  |

- 1) IPC-6012E-EN Table 3-15: External Conductior Thickness after Plating

- 2) Extra cost: No standard copper foil

- 3) Outer layers: only possible with uniform circuit layout

| Inner layers - conductor spacing                                           |                                       |  |                                                     |                  |         |

|----------------------------------------------------------------------------|---------------------------------------|--|-----------------------------------------------------|------------------|---------|

| Starting foil                                                              | Minimum copper thickness <sup>4</sup> |  |                                                     | Minimum          | Minimum |

| thickness                                                                  | IPC-class<br>1, 2, 3                  |  | conductor conducto<br>spacing Standard spacing Adva | spacing Advanced |         |

| 17,1 µm [1/2 oz.]                                                          | 11,4 µm                               |  |                                                     | 100 µm           | 75 µm   |

| 34,3 µm [1 oz.]                                                            | 24,9 μm                               |  |                                                     | 120 µm           | 100 µm  |

| 68,6 µm [2 oz.]                                                            | 55,7 µm                               |  |                                                     | 180 µm           | 150 µm  |

| 102,9 μm [3 oz.]                                                           | 86,6 µm                               |  |                                                     | 250 µm           | 225 µm  |

| 4) IPC-6012E-EN Table 3-14: Internal Layer Foil Thickness after Processing |                                       |  |                                                     |                  |         |

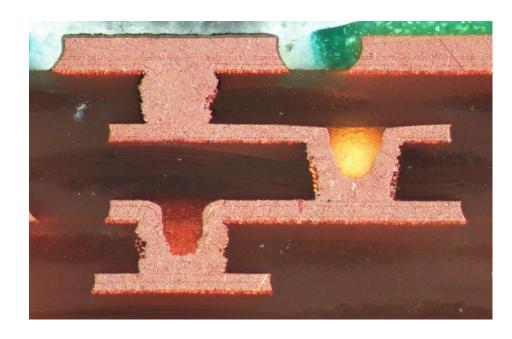

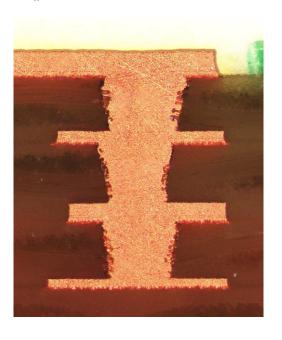

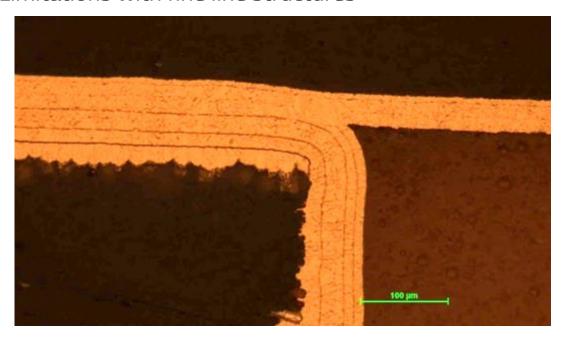

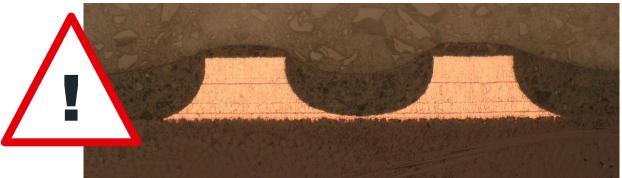

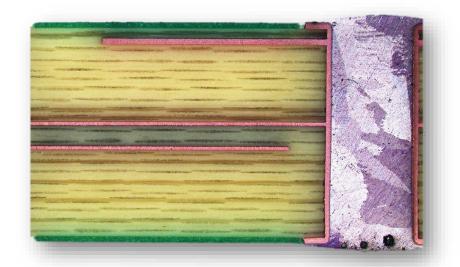

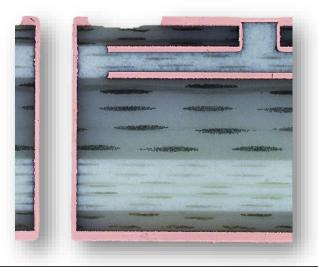

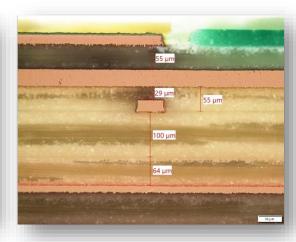

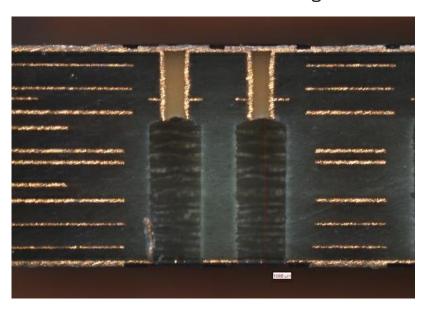

### FILLED VIA – TECHNOLOGY COMBINATION

#### Limitations with fine line structures

Due to repeated electroplating, the copper rises on the surface. This means that compromises in the structure sizes are sometimes necessary.

| Typical design parameters depending on the Cu thickness |            |        |  |  |  |  |  |

|---------------------------------------------------------|------------|--------|--|--|--|--|--|

| Copper-Thickness                                        | Line width | Space  |  |  |  |  |  |

| ~ 30 µm                                                 | 100 µm     | 100 µm |  |  |  |  |  |

| ~ 40 µm                                                 | 125 μm     | 120 µm |  |  |  |  |  |

| ~ 50 µm                                                 | 150 µm     | 180 µm |  |  |  |  |  |

### <u>IMPEDANCE – INFLUENCING FACTORS</u>

$Z_L$  = Impedance

$E_r = Dk = Dielectric Constant$

h = Dielectric Thickness

w = Track Width

t = Track Thickness

w+h = Designer + PCB manufacturer

t = Electroplating process, base copper

$\varepsilon_r$  = Base Material

## **BEST COMBINATION?**

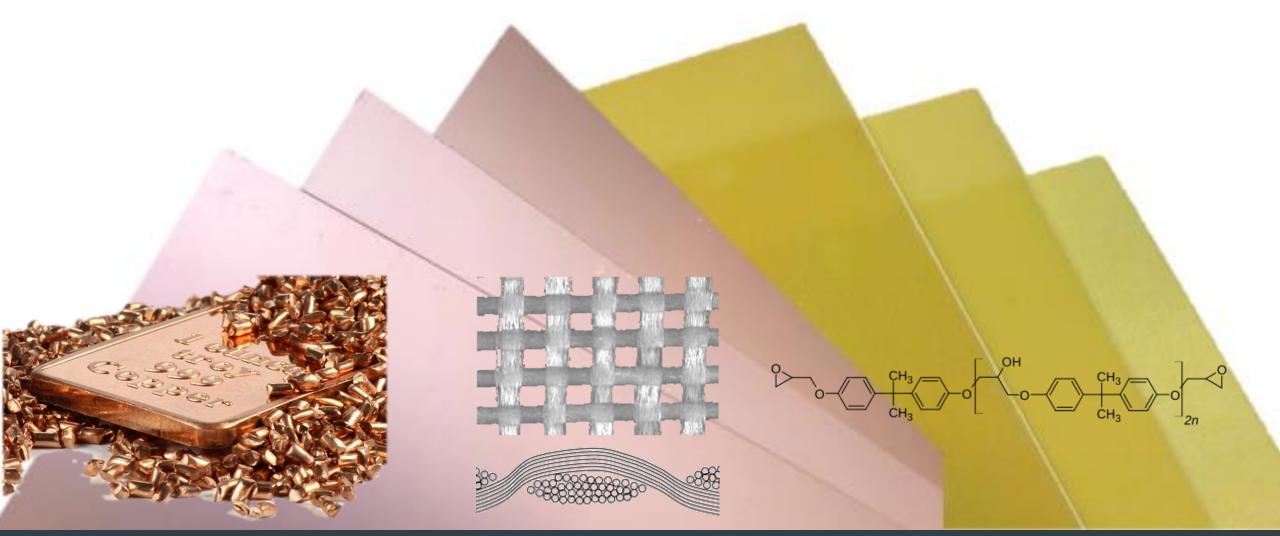

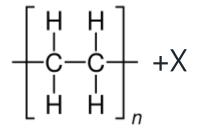

## **BASE MATERIAL FR4**

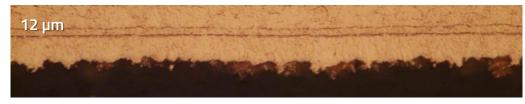

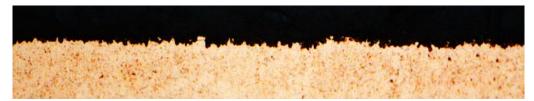

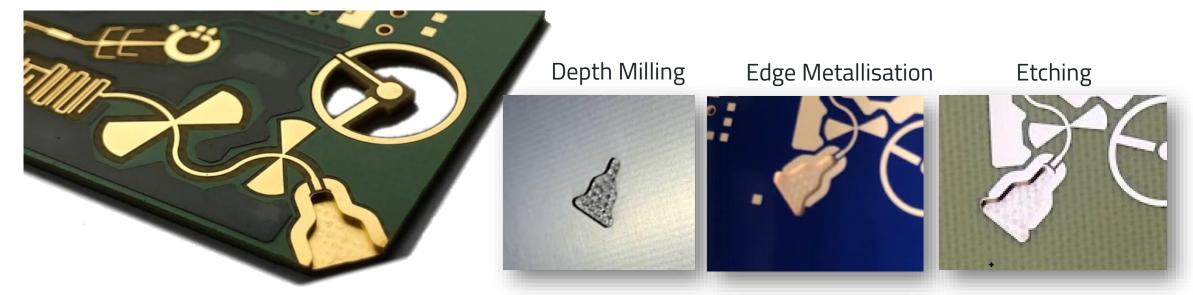

### **COPPERFOIL ROUGHNESS**

#### Treatment

#### Shine + Adhesion Promoter

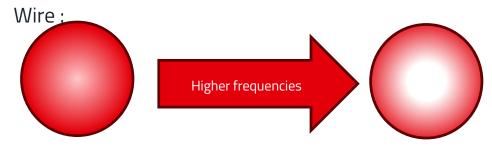

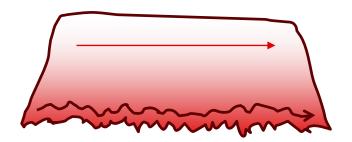

#### Skin-Effect

In simple terms, the skin effect is the tendency for alternating current (AC) to flow mostly near the outer surface (or "skin") of a conductor, rather than throughout its entire cross-section, especially at higher frequencies ~ 3 Ghz and more.

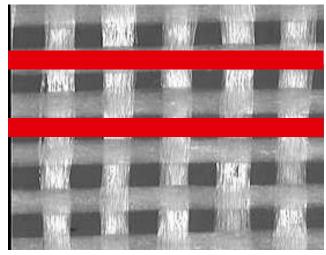

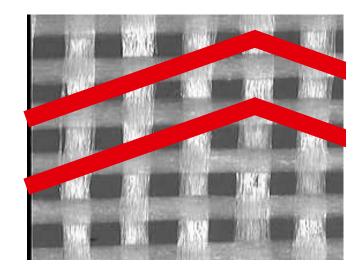

### **CONSTRUCTION OF PREPREG**

#### Example values

FR4 Prepreg 106

Thickness 50 µm  $\varepsilon_{\rm r} = 2.8 - 3.7$ Resin content ~70%

FR4 Prepreg 2116

Thickness 90 – 110 µm  $\varepsilon_{\rm r} = 3.6 - 3.8$ Resin content ~50%

FR4 Prepreg 1080

Thickness 60 - 70 µm  $\varepsilon_{\rm r} = 3.2 - 3.7$ Resin content ~60%

FR4 Prepreg 7628

Thickness 170 – 190 μm  $\varepsilon_{\rm r} = 4.1 - 4.6$ Resin content ~45%

glass  $\varepsilon r \sim 6,1 / resin \varepsilon r \sim 3,2$ Cores are laminated Prepreg

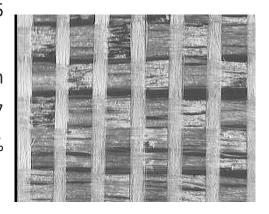

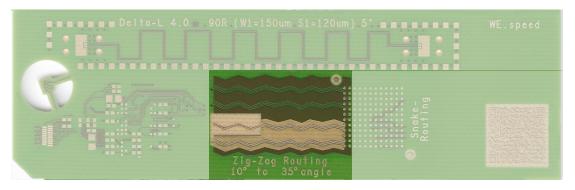

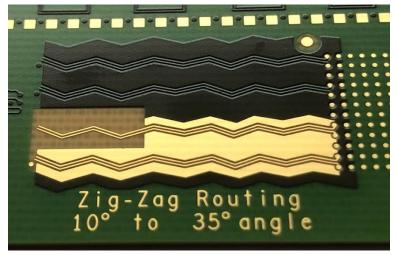

#### Zig-Zag Routing

- Minimize Fiber-Weave Effect Dk / E<sub>R</sub> Glas ~6.1 Dk / E<sub>R</sub> Fr4-Resin ~3.2

- Used in Customer application **WEdesign** Team 20-22-GHz

### **MATERIAL COMPARISION**

FR4

**Epoxy-Resin**

- Tg 130 180°C

- Dk 4.37 Df 0.022 at 1 GHz

- Without or with Fillers

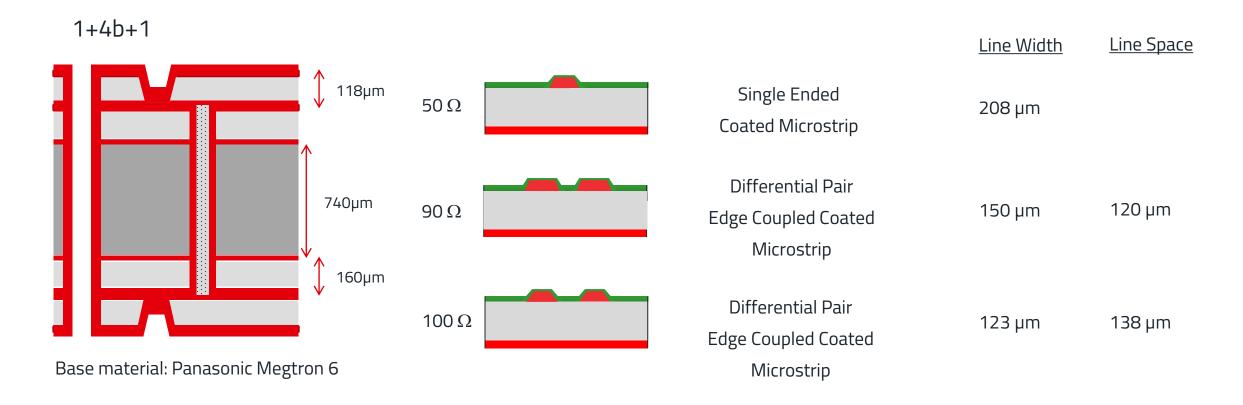

Megtron 6 PPE-Resin

- Tg 185°C

- Dk 3.61 Df 0.0040 at 10 GHz

- With Fillers

Rogers Hydrod

Hydrocabon-Resin

- Tg > 280°C

- Dk 3.48 Df 0.0037 at 10 GHz

- With ceramic Fillers

### **MATERIAL COMPARISION**

Impact of new Materials

**Raw Material**

**Wet Processes**

**Multilayer Pressing**

**Drill Parameters**

Price increase

4x - 20x

to Tg150 Material

Higher temperature and more time necessary

Higher wear out of drill bits

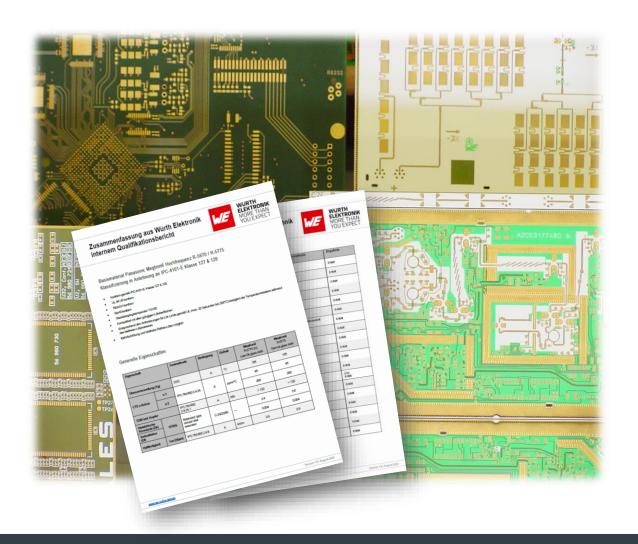

## **QUALIFIED MATERIALS**

For analog and digital High Speed applications

Dk 3.61

Dissipation factor 0.0040 at 10 GHz

For special applications

4000-Family

Dk of 3.48

Dissipation factor of 0.0037 @10 GHz

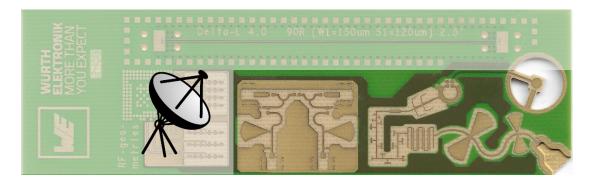

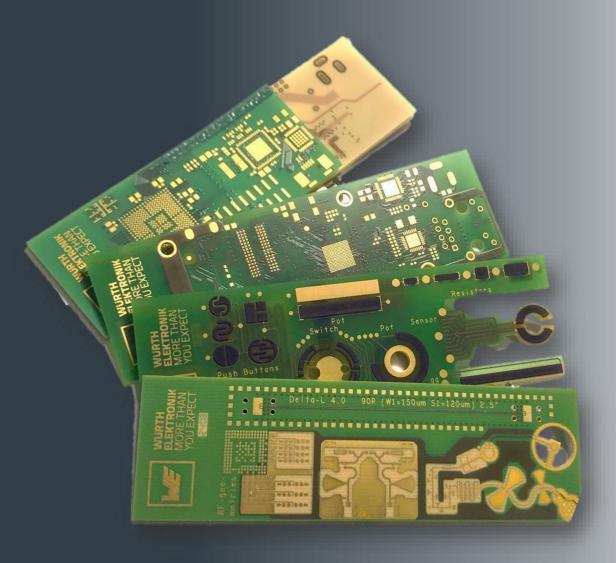

### Get your personal sample NOW

https://www.we-online.com/we-speed

Stackup

SUPPORT: If you need an Impedance controlled Stack up feel free to contact us hdi@we-online.com

HDI-Design

HDI- Approach

Back Drilling

#### Use Micro Via as much as possible

- Small footprint

- Short stub length

- In volume minimal extra cost → Stitching Via

- More reliable than Back Drilling

RF Filters & Antennas

Be creative!

Possible Connection for a waveguide

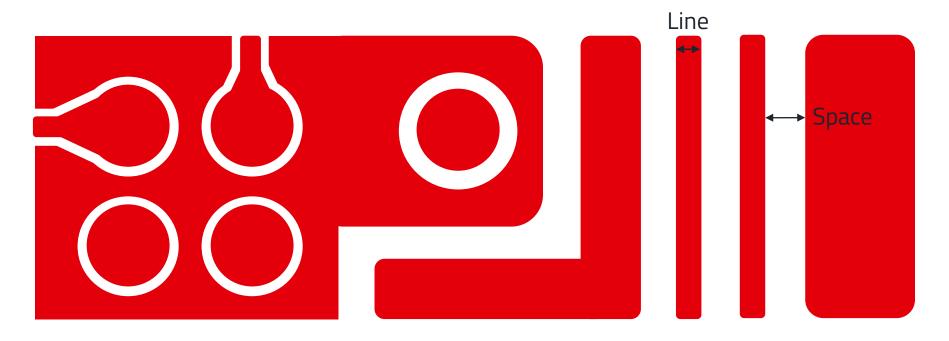

### **LINE/SPACE DEPENDENCY - PRACTICAL EXAMPLE**

In narrow spaces: small conductor spacing

Rest of the layout: generous spacing New data formats: Use attributes Asymmetric layout definition

Line/Space

Not  $100/100 \mu m$

but 80/120 μm

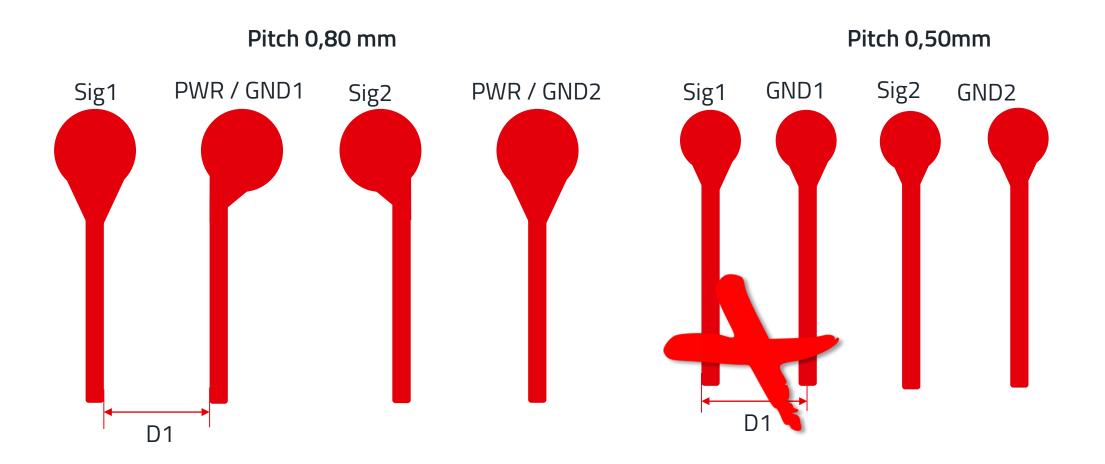

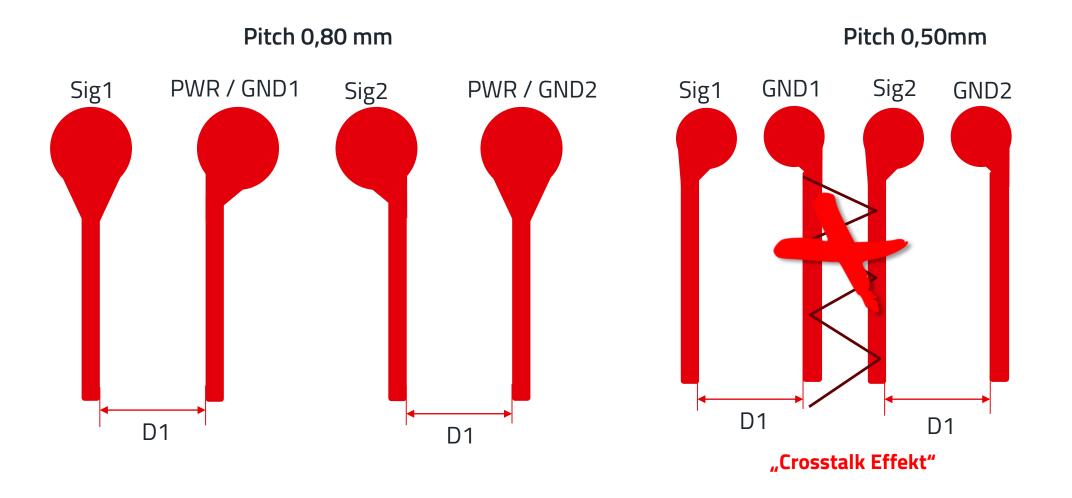

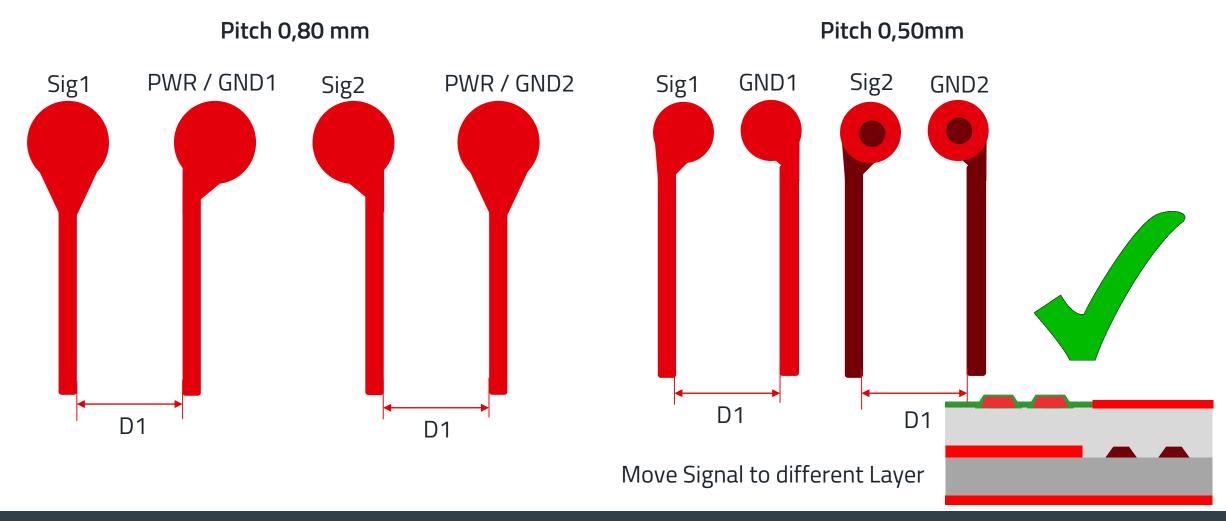

## PITCH DEPENDENCY - PRACTICAL EXAMPLE

### PITCH DEPENDENCY - PRACTICAL EXAMPLE

### PITCH DEPENDENCY - PRACTICAL EXAMPLE

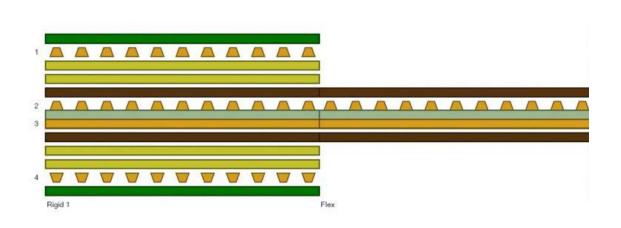

## **FLEXIBLE STACKUP**

### Seperate Calculation neccesary!

#### Closed Return Path in Flex Area?

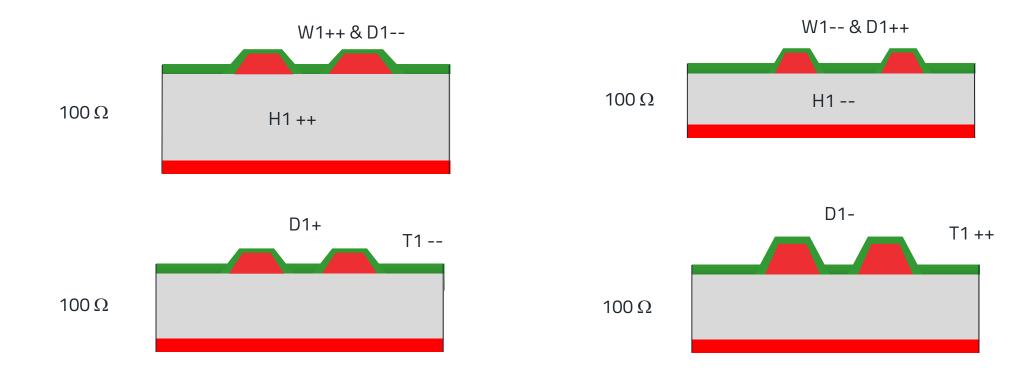

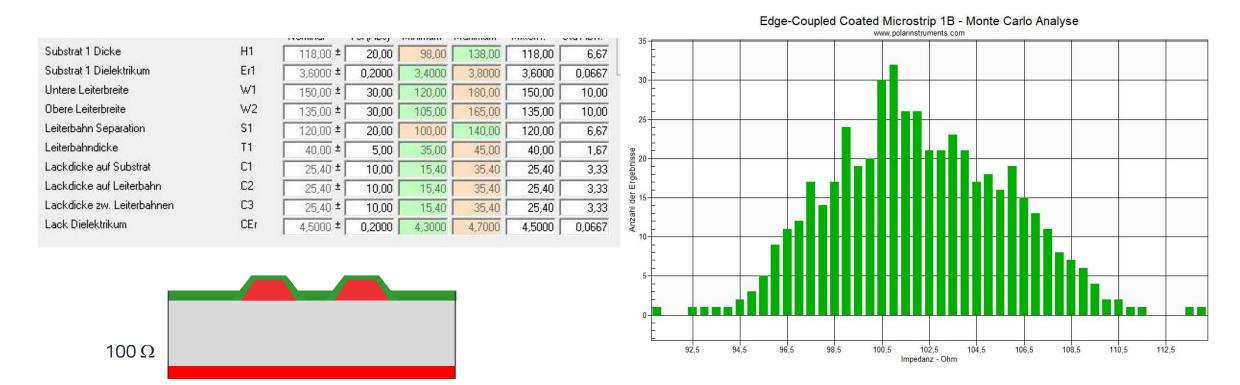

### WHAT HAPPENS WHEN TOLARANCES HIT YOU?

#### Monte Carlo Simulation

With IPC - Tolerance Addition in a Worst Case Scenario the Impedance can be out of Specification - so careful and reliable Parameter finding is needed

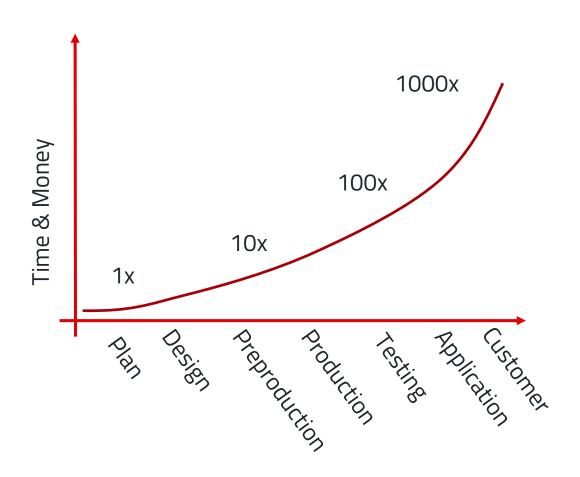

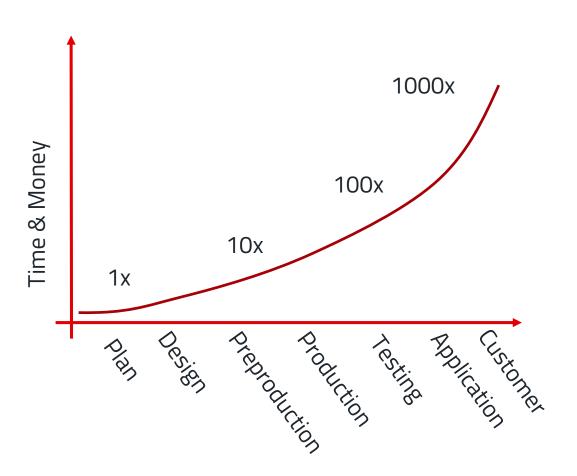

### **SUMMARY**

#### Approach to a new High Speed Design:

- Experience?

- Competence?

- Trial & Error?

- Simulate before Fabricate?

### **SUMMARY**

#### Approach to a new High Speed Design:

- Plan Impedance controlled Stack Up

- Design

Preproduction

Feasibility & DRC Check **EQ-Process with Documentation**

- **Production**

- **Quality Control** "Design In" if necessary

- **Testing** Impedance Control on every production panel

### **SUMMARY**

- Würth Elektronik has High Speed Material qualified

- Panasonic Megtron 6

- Many others are available with WE-Asia

- WE can measure Material- and Layout parameters

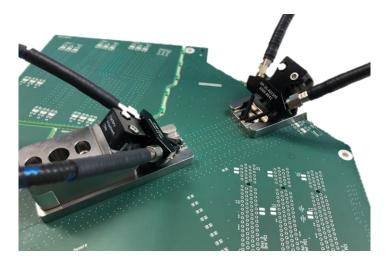

- Polar CITS880s Impedance Meter

- Polar Atlas Delta L4.0 VNA Meter

- WE offers custom impedance controlled Stackups

- More than 20 years of experience

- High Speed Designs can be complex an early discussion about the Topic will lead to an optimal Solution